参考的书《计算机组成与体系结构》第4版(黑皮书)(The Essentials of Computer Organization and Architecture)。注:目前仅记录考试需要用到的部分。

4.2CPU

作用

- 取指fetch

- 译码decode

- 执行execute指令

组成

- 数据通路datapath

- ALU:arithmetic and logic unit算术逻辑单元

- register寄存器/存储单元

- bus数据总线

- 控制单元control unit

寄存器

寄存器中存放的数据易于CPU访问,可以使用 D 触发器来实现。

ALU

算术逻辑单元 (ALU) 按照控制单元的指示执行逻辑和算术运算。

控制单元

控制单元根据程序计数器寄存器和状态寄存器中的值确定执行哪些action

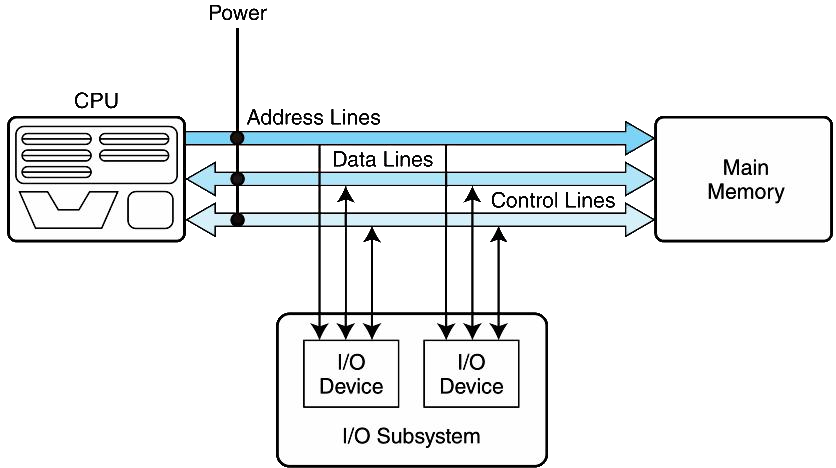

4.3总线

分类

- 点对点总线point-to-point

- 多点总线multipoint

组成

- 数据线data lines:传送位bit

- 控制线control lines:控制数据流的方向+设备的访问控制

- 地址线address lines:确定数据源或目标的位置

总线仲裁

在主从配置中,不止一个设备可以是总线主机,并发的总线主机请求必须进行仲裁

- daisy chain:根据优先级

- centralized parallel:集中并行:每个设备直接连接到一个仲裁电路。

- distributed using self-detection:使用自我检测进行分布式:设备在它们之间决定哪一个获得总线。

- distributed using collision-detection:分布式使用冲突检测:任何设备都可以尝试使用总线。如果它的数据与另一个设备的数据冲突,它会重试

4.4时钟

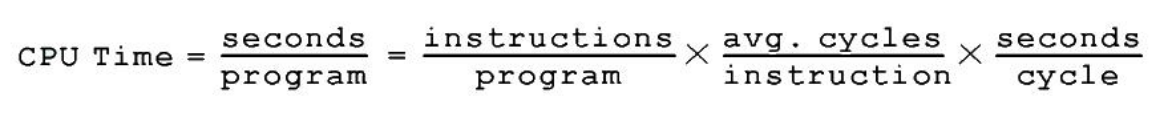

clock cycle时钟周期= 1 / 频率。在一个时钟周期内,CPU仅完成一个最基本的动作

clock frequency时钟频率:决定执行所有操作的速度

指令周期数CPI:平均每条指令耗费的时钟周期数

- CPI = 执行程序所需的时钟周期数 / 所执行的指令条数

运行程序所需的CPU时间:

- CPU时间 = 执行程序所需的时钟周期数 * 时钟周期时间

4.6存储器

- memory由类似于寄存器的可寻址addressable存储单元storage cells的线性阵列linear array组成

- 按字节寻址或字寻址

- memory由RAM芯片构成,通常以长度×宽度来表示

地址表示

eg.假设一个memory由16个2K×8位芯片组成,则:

- 假设按字节(8bit)寻址,则memory=$16×2K=2^4×2×2^{10}=2^{15}$,即每个地址需要15位来表示

- 由16个芯片=$2^4$,即需要4位来选择芯片

- 需要(15-4=)11位来表示选中芯片内的偏移量

- 高阶交错high-order interleaving:高4位来选择芯片

- 低阶交错:低4位

- ps:注意存储器的寻址方式(按字or字节)

4.7中断

Interrupts, higher-priority更高优先级

被触发triggered

- I/O请求request

- 算术错误arithmetic errors

- 遇到无效指令invalid instruction

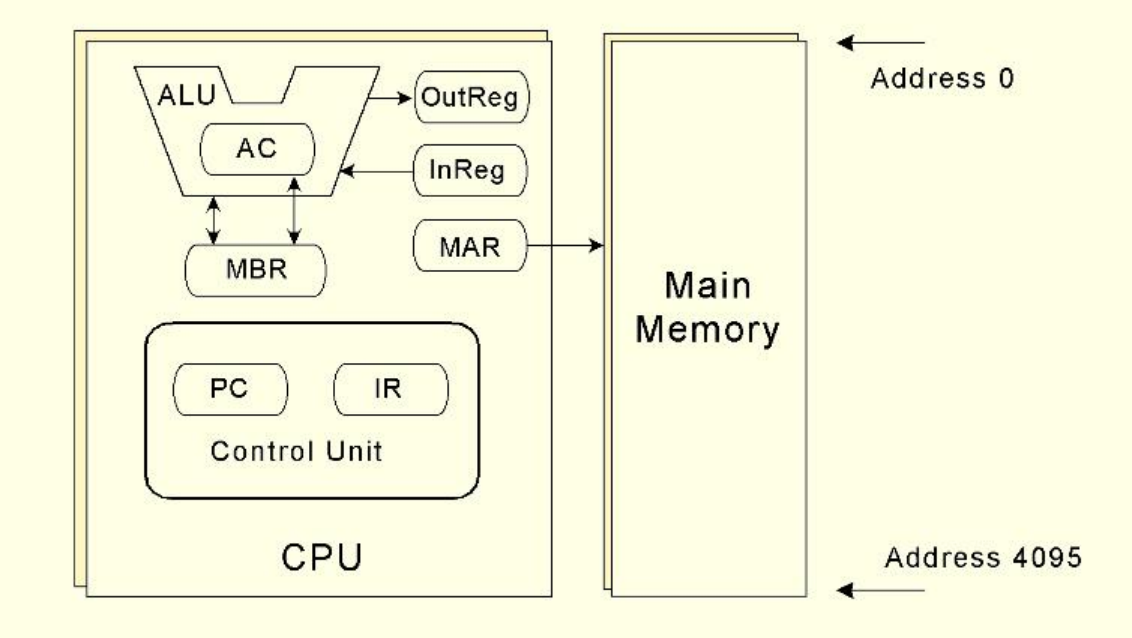

4.8MARIE

MARIE架构特性:

二进制及补码表示

存储程序、固定字长、指令

主存可字寻址,总容量4K字

1字=16位

16位指令=4位操作码+12位地址

16位ALU

7个寄存器,用于控制和数据移动(没特别提到就是16位)

- AC,累加器accumulator

- MAR,内存地址寄存器memory address register,12位

- MBR,内存缓冲寄存器memory buffer register

- PC,程序计数器program counter,12位,存储指令的地址

- IR,指令寄存器instruction register

- InREG,输入寄存器input register,8位

- OutREG,输出寄存器output register,8位

RTL寄存器传输语言,用M[X]表示存储在寄存器X中的实际数字值

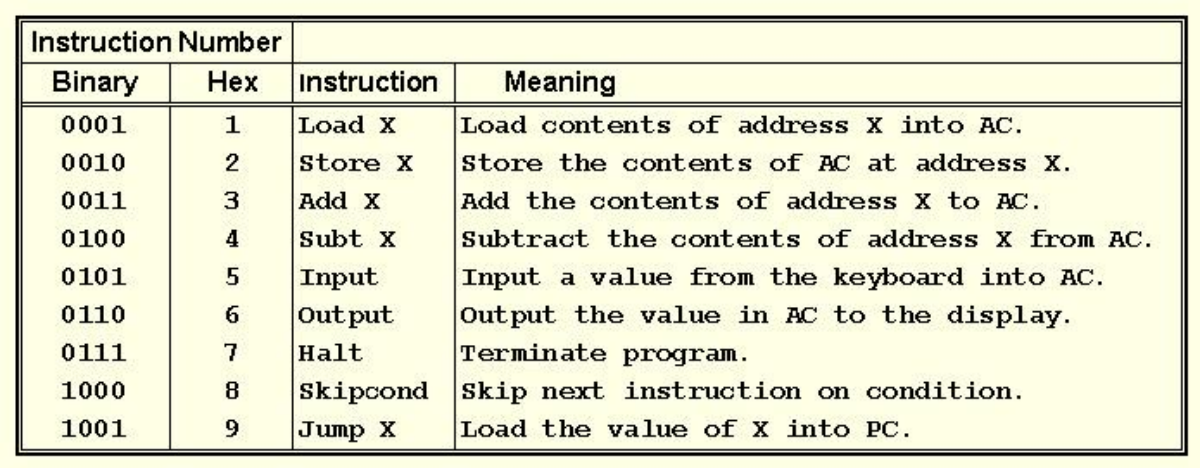

指令集架构

instruction set architecture:ISA,是硬件与软件之间的接口,MARIE模型只包含13条指令,每条指令由一系列更小的指令组成(即微操作microoperations)

一些基本的MARIE指令:计算机组成和体系结构【4】MARIE机器_(∪.∪ )…zzz的博客-CSDN博客_marie汇编语言

- AC:累加寄存器

- Load:将地址X中的值存入AC

- Store:将AC中的值存到地址X中

- Add:AC+=地址X中的值

- Subt:AC-=地址X中的值

- Skipcond:如果AC中的值大于0则跳过下一条指令

- Jump:将X装入PC(程序计数器,即转到X作为下一条指令)

- Clear:AC=0

- ADDI X:(间接寻址),将地址X中的值作为地址Y,AC+=地址Y中的值

4.9指令处理

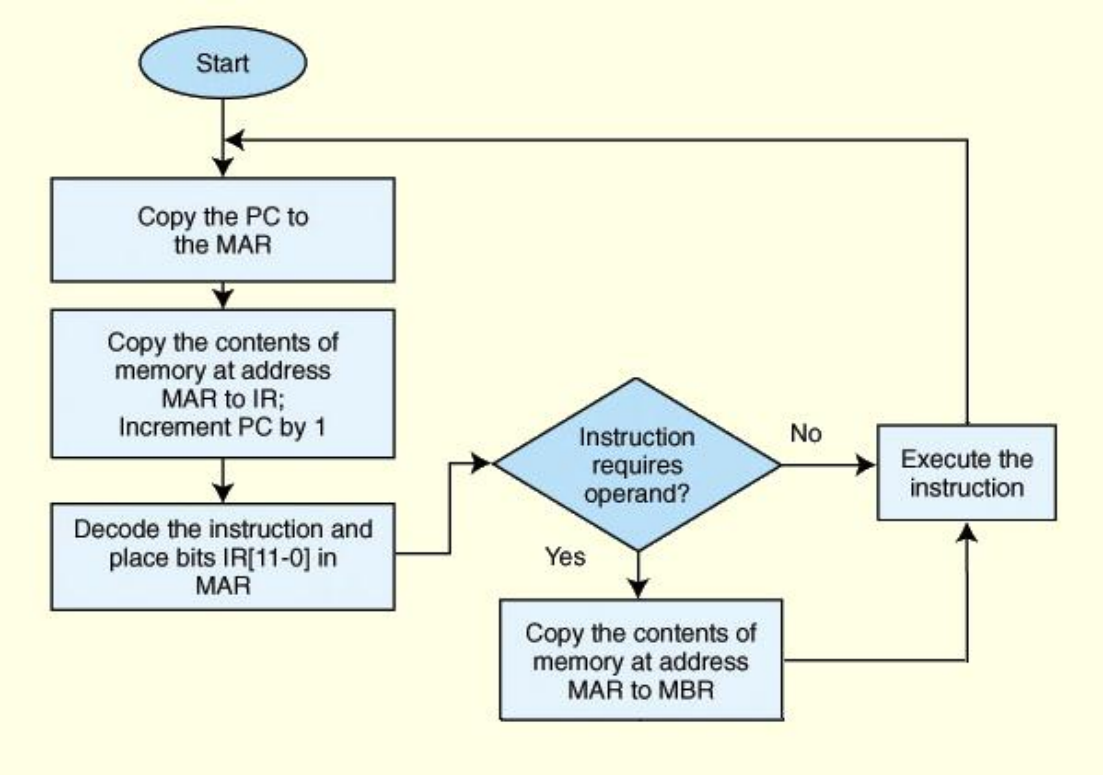

取指-译码-执行周期

- 从内存中取指并放入IR

- 进入IR后,解码

- 如果涉及操作数,则取出操作数放入MBR

中断指令

4.10一个简单的程序

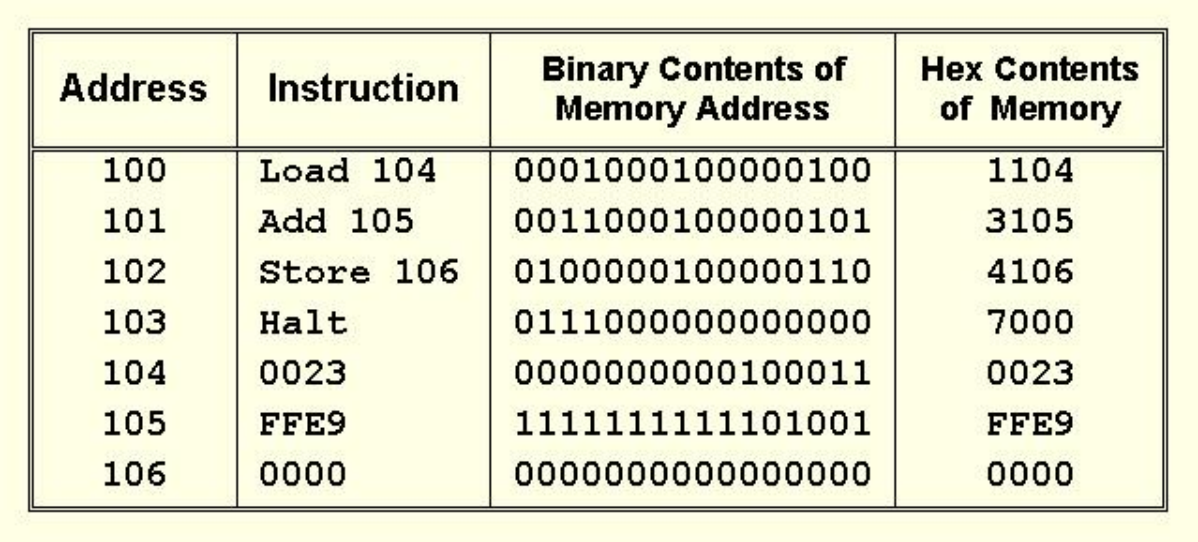

假设部分地址及其内容:

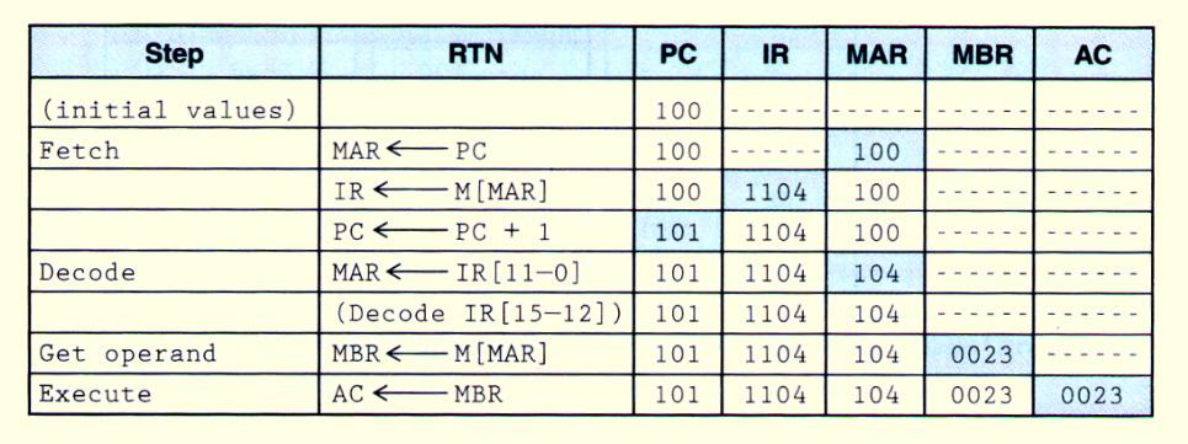

Load 104指令执行的具体情况-寄存器的变化:

- 取指

- 从PC中取出指令放到MAR;

- 将MAR中的指令地址中的指令内容(hex)传入IR;

- PC++(程序计数器自动更新下一条指令的位置)

- 解码

- 将IR中的指令的地址部分(IR[11-0]共12位)传入MAR

- 解码操作数(IR[15-12])

- 获取操作数:将MAR中的内容传入MBR

- 执行指令,将MBR中的值放入AC

作业

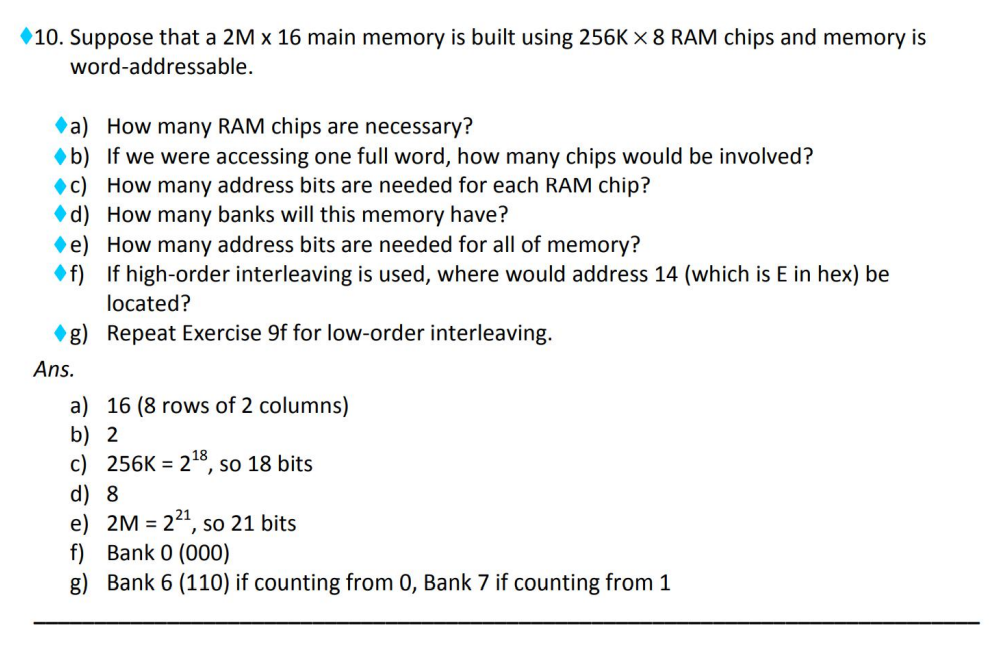

10.存储寻址

首先关注题中是否提到是按字还是按字节寻址

- 需要的RAM芯片数量:根据主存容量的长和宽共同确定

- 地址位数=幂次数

- 芯片的地址位好像不需要考虑按什么编址?就一行算一个存储单元

- emmm那就是看有多少行吧

- 存储体:主存按行分模块

- n路交叉表示将主存分为n块

- 本题好像没说啥就直接按照芯片分块了?

- 高/低位交叉编址

- 块字段+偏移字段

- 一个位置返回一个字

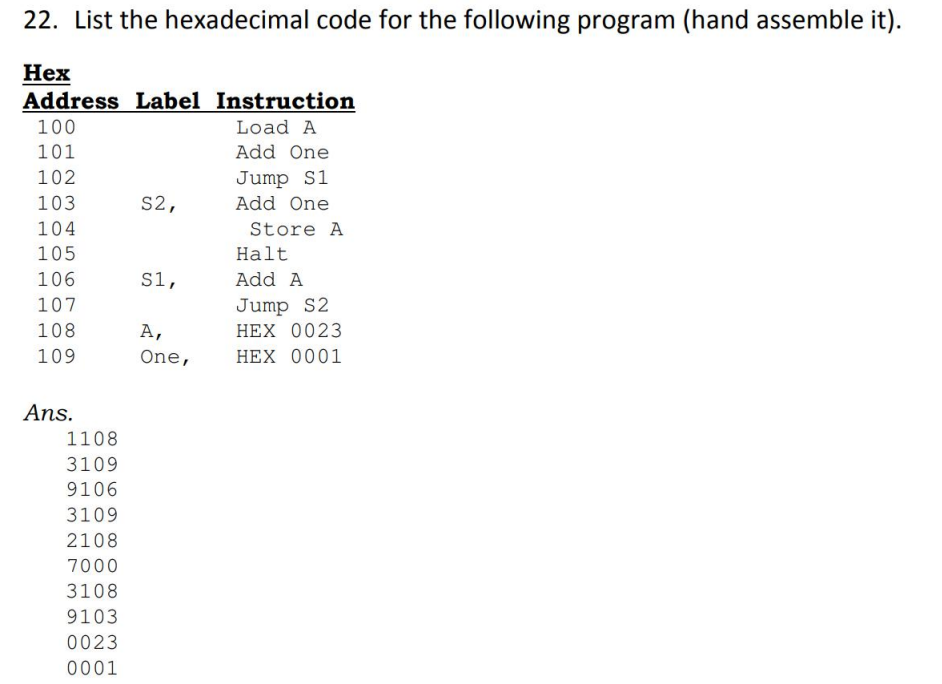

22.指令的16进制表示

前4位是操作码如LOAD,后12是操作数如地址

- Load A: Load=0001=0x1, A=0x108→0x1108

- Halt没有操作数,则为0

- HEX 0001没有操作码

23.符号表

symbol table,就是用一个符号表示一个地址以上一题为例:

| A | 108 |

|---|---|

| One | 109 |

| S1 | 106 |

| S2 | 103 |

24.AC寄存器

与指令执行,直接寻址,间接寻址有关