参考的书《计算机组成与体系结构》第4版(黑皮书)(The Essentials of Computer Organization and Architecture)。注:目前仅记录考试需要用到的部分。

5.2指令格式

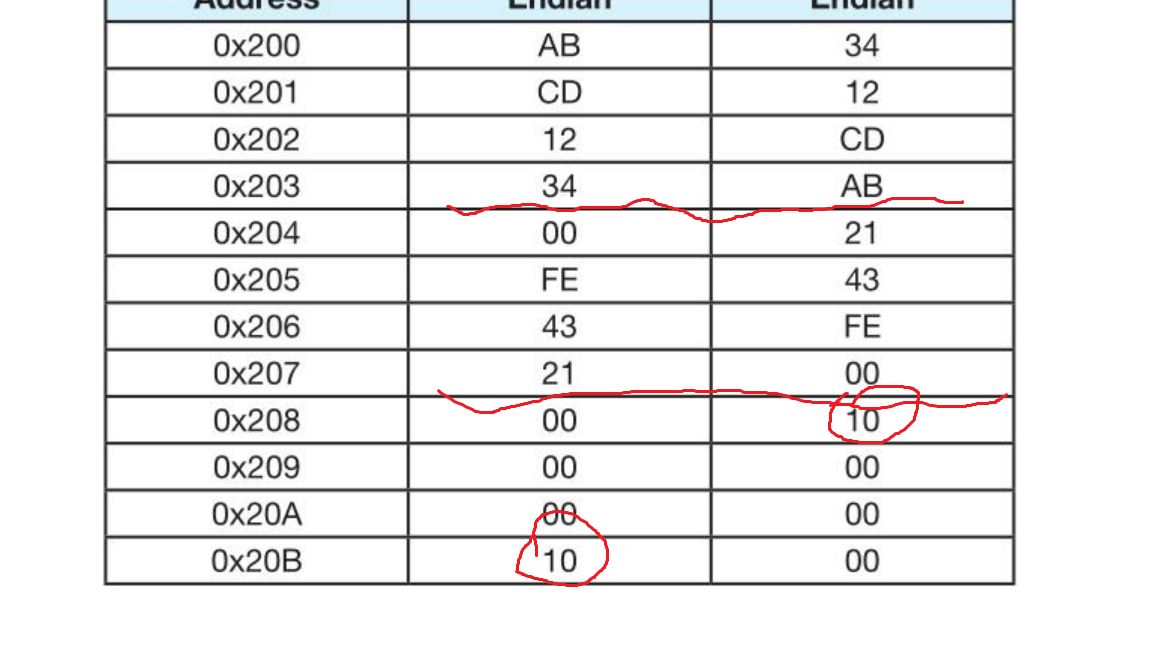

大端小端

- 大端big endian存储:低地址存高字节,可在低地址处判断正负

- 小端:16位转32位不需要变化

eg.使用32bit,存储value: 0xABCD1234, 0x00FE4321, 0x10,从地址0x200开始:

注意上图中0x10的存储,不足32bit补零。此时可明显看出若采用16位存储,大端方式需要变化而小端不用。

架构

- 堆栈架构stack:指令和操作数从堆栈中获取,堆栈不可随机访问

- 累加器架构accumulator:二元运算的一个操作数隐含在累加器中,另一个在内存中,造成大量总线流量

- 通用寄存器架构general purpose register(GPR)

- 比累加器架构更快

- 编译器的有效实现

- 更长的指令

堆栈

二进制指令(ADD, MULT)使用堆栈上的顶部两项,要求使用后缀表示法即逆波兰式。计算$Z=XY×WU×+$(后缀表达式)

1 | PUSH X |

不同操作数的ISA执行算术

eg.计算$Z=X×Y+W×U$(中缀表达式),用R表示寄存器

三地址ISA(eg.大型机)

1

2

3MULT R1,X,Y

MULT R2,W,U

ADD Z,R1,R2双地址ISA(eg.Intel),双地址ISA通常要求一个操作数是寄存器

1

2

3

4

5

6LOAD R1,X

MULT R1,Y

LOAD R2,W

MULT R2,U

ADD R1,R2

STORE Z,R1单地址ISA(eg.MARIE),其中一个操作数隐含在累加器中?

1

2

3

4

5

6

7LOAD X

MULT Y

STORE TEMP

LOAD W

MULT U

ADD TEMP

STORE Z

扩展操作码

通过改变操作码的长度和使用转义操作码实现多种多样的指令集。

eg.8位指令可以构成:

- 3条 3位双操作数

- 2条 4位单操作数

- 4条 3位单操作数

5.3指令类型

- data movement

- arithmetic

- boolean

- bit manipulation

- I/O

- control transfer

- special purpose

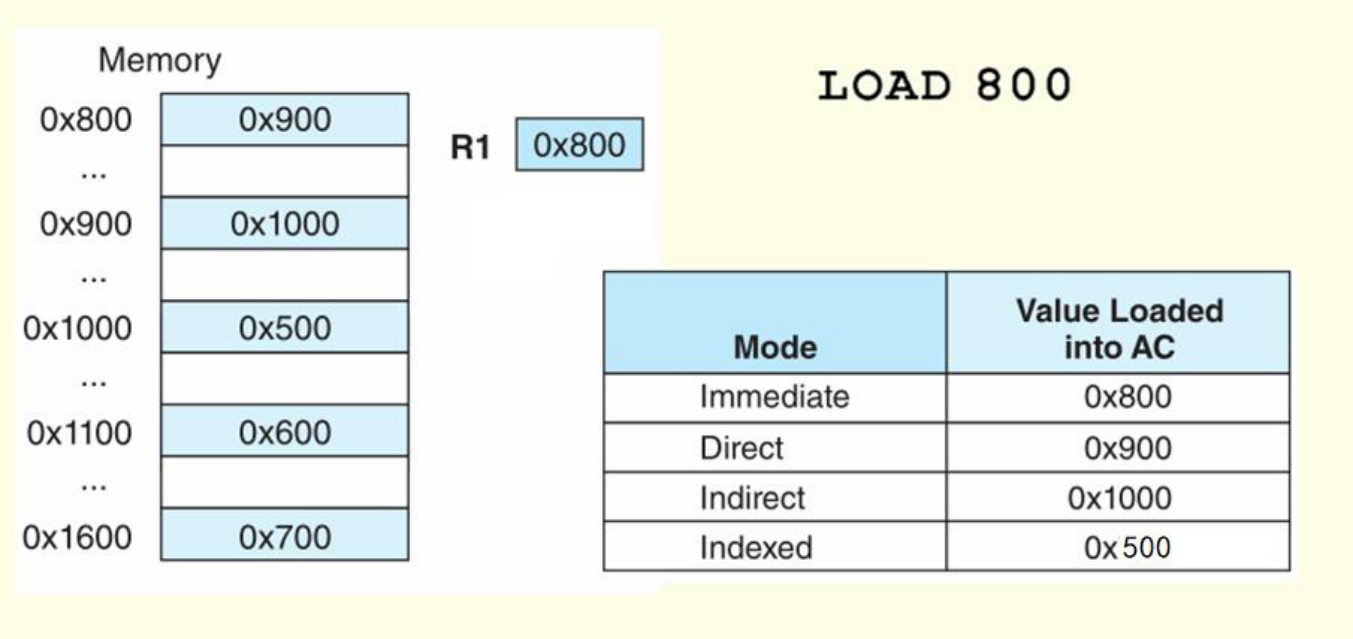

5.4寻址

Addressing

- 立即寻址immediate addressing:数据是指令的一部分(即操作数就是真正的数值)

- 直接寻址direct:操作数是数据地址

- 寄存器寻址register:操作数是数据在寄存器中的位置

- 间接寻址indirect:操作数是数据地址的地址(套娃?

- 寄存器间接寻址register indirect:操作数是数据地址在寄存器中的位置

- 索引寻址indexed:操作数是地址,最终有效地址=操作数+指定偏移量(存于某寄存器如图中的R1)

- 基址寻址based:与indexed类似,区别在于indexed中的寄存器用来保存偏移量,based中的寄存器用来保存基地址。

eg.LOAD 800, R1 0x800(offset)

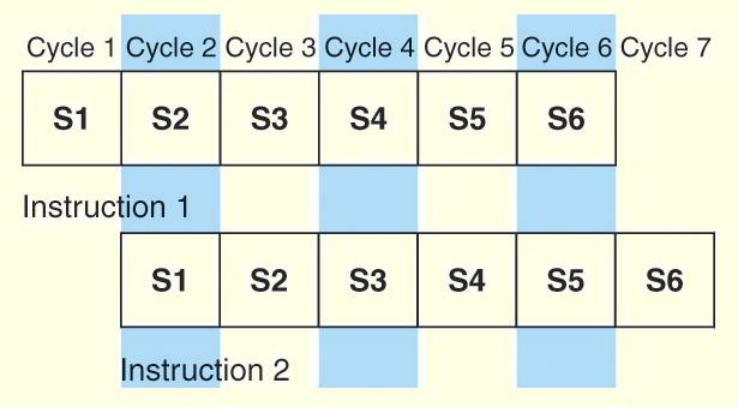

5.5指令流水线

instruction pipelining

将指令执行周期分为更小的步骤:

- 获取指令fetch

- 解码操作码decode opcode

- 计算有效操作数的地址(寻址?)

- 获取操作数operands

- 执行指令execute

- 存储结果store

这些较小的步骤可以并行执行以增加吞吐量,每个时钟周期执行一小步,且阶段重叠:

加速比

eg.假设共有n条指令,一条指令由k个小步骤组成,执行一个阶段用时$t_p$。即共用时:

$$

(k×t_p)+(n-1)t_p=(k+n-1)t_p

$$

加速比:$Speedup S=\frac{nkt_p}{(k+n-1)t_p}$

当n趋于无穷大,(k+n-1)→n,得到利率加速比=k

pipeline停止或刷新

- 资源冲突

- 数据依赖

- 条件分支

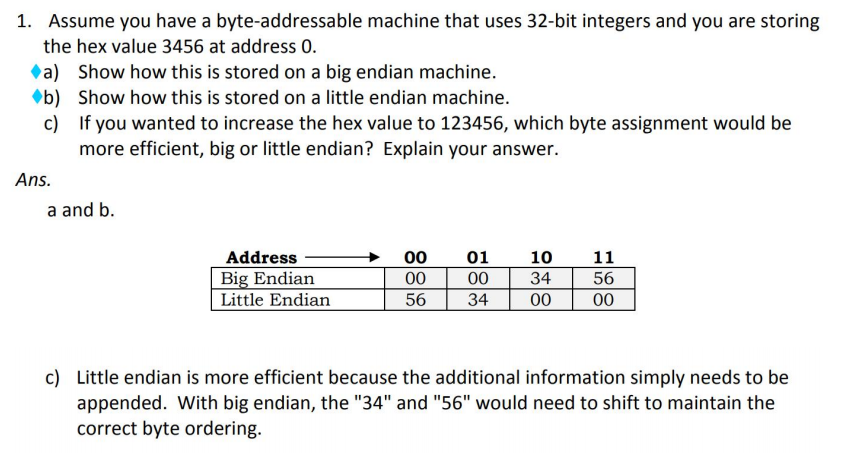

作业

1.大端小端

注意看位数不足时的操作

c)why?小端更好?

16.堆栈算术

- 逆波兰式

- 转为指令:单地址,默认隐含堆栈

- Push、Subtract、Mult、Add、Div、Pop

17.指令数量

- 判断是否可能可以

- 计算总共需要多少位=指令条数×2^地址位数

- 与主存容量对比

- 如果可能,尝试写出

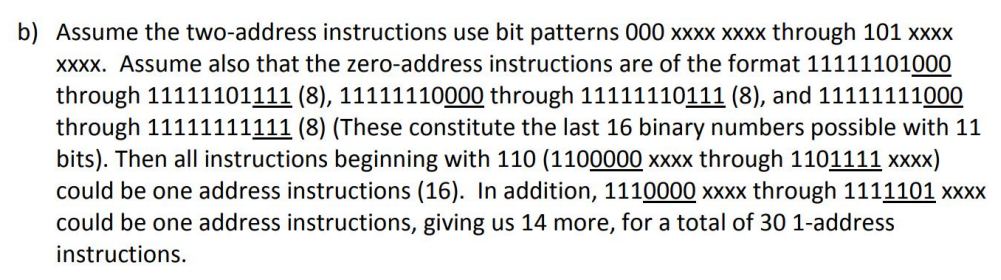

- 妙啊,上图

题中说已有双地址和零地址指令,那就从两头减?

21.寻址

立即、直接、间接、索引

29.指令流水线

分别计算用的时间,需要根据实际情况判断当指令数为多少时二者用时相等。